A szimmetrikus többprocesszoros feldolgozás (SMP) egy olyan architektúra, ahol több processzor osztozik egyetlen főmemórián és I/O eszközökön. Lényeges eleme, hogy minden processzor egyenlő hozzáféréssel rendelkezik a rendszer erőforrásaihoz. Ez lehetővé teszi a feladatok párhuzamos végrehajtását, ami jelentősen növeli a számítási teljesítményt.

Az SMP rendszerekben minden processzor ugyanazt az operációs rendszert futtatja, és a feladatok elosztása a processzorok között dinamikusan történik. Ez azt jelenti, hogy az operációs rendszer képes a terhelést egyenletesen elosztani, kihasználva az összes rendelkezésre álló processzort.

Az SMP lényege, hogy a rendszer erőforrásait minden processzor egyenlően használhatja, ezzel maximalizálva a párhuzamos feldolgozást.

A hatékony SMP működéshez elengedhetetlen a cache koherencia biztosítása. Mivel minden processzor rendelkezik saját gyorsítótárral, a memóriában tárolt adatok több példányban is létezhetnek. A cache koherencia protokollok biztosítják, hogy az adatok konzisztensek maradjanak, függetlenül attól, hogy melyik processzor fér hozzájuk.

Az SMP rendszerek skálázhatósága korlátozott. Ahogy a processzorok száma nő, a memória és az I/O eszközök iránti igény is növekszik, ami szűk keresztmetszeteket okozhat. Mindazonáltal az SMP továbbra is egy fontos technológia a nagy teljesítményű számítástechnikában, különösen olyan alkalmazások esetében, amelyek jól párhuzamosíthatók.

Az SMP architektúra definíciója és főbb jellemzői

A szimmetrikus többprocesszoros feldolgozás (SMP) egy olyan számítógépes architektúra, amelyben több azonos típusú processzor osztozik a közös memórián és az I/O eszközökön. Ez azt jelenti, hogy minden processzor egyenlő hozzáféréssel rendelkezik a rendszer erőforrásaihoz, és bármelyik processzor képes bármelyik feladatot végrehajtani.

Az SMP rendszerekben a processzorok együttműködnek a feladatok elvégzésében, ami jelentősen javíthatja a teljesítményt. A feladatok párhuzamosítása lehetővé teszi, hogy több processzor egyszerre dolgozzon ugyanazon a problémán, ezáltal csökkentve a végrehajtási időt.

Az SMP egyik legfontosabb jellemzője a közös memória használata, ami lehetővé teszi a processzorok közötti gyors és hatékony adatcserét.

Az SMP rendszerek skálázhatósága korlátozott lehet. Ahogy a processzorok száma növekszik, a közös memória elérése egyre nagyobb szűk keresztmetszetet jelenthet, ami csökkentheti a rendszer hatékonyságát. Ezt a problémát a cache koherencia protokollok és a NUMA (Non-Uniform Memory Access) architektúrák próbálják enyhíteni.

Az SMP rendszerek operációs rendszere speciális támogatást igényel. Az operációs rendszernek képesnek kell lennie a feladatok elosztására a processzorok között, és biztosítania kell a processzorok közötti szinkronizációt és kommunikációt. Ezen kívül, az operációs rendszernek kezelnie kell a közös erőforrásokhoz való hozzáférést, hogy elkerülje a konfliktusokat és a holtpontokat.

Az SMP architektúra előnyei közé tartozik a nagyobb számítási teljesítmény, a jobb válaszidő és a megnövelt rendelkezésre állás. Ugyanakkor az SMP rendszerek bonyolultabbak és drágábbak lehetnek, mint az egyprocesszoros rendszerek.

Az SMP rendszerek előnyei és hátrányai a párhuzamos feldolgozásban

A szimmetrikus többprocesszoros rendszerek (SMP) jelentős előnyökkel járnak a párhuzamos feldolgozás terén. Az egyik legfontosabb előny a jobb erőforrás-kihasználás. Mivel minden processzor egyenlő hozzáféréssel rendelkezik a memóriához és a perifériákhoz, a feladatok dinamikusan oszthatók el a rendelkezésre álló processzorok között, elkerülve az egyes processzorok terheltségét, miközben mások tétlenek.

Ez a megközelítés növeli a rendszer átviteli sebességét és csökkenti a válaszidőt, különösen olyan alkalmazások esetén, amelyek sok párhuzamosan futtatható feladatra bonthatók. Egy másik előny a fokozott hibatűrés. Ha egy processzor meghibásodik, a többi processzor átveheti a feladatait, minimalizálva az állásidőt és biztosítva a rendszer folyamatos működését. Ez kritikus fontosságú olyan alkalmazásoknál, ahol a folyamatos rendelkezésre állás elengedhetetlen.

Az SMP rendszerek egyik legnagyobb előnye, hogy képesek kihasználni a többmagos processzorok nyújtotta potenciált, lehetővé téve a valódi párhuzamos feldolgozást.

Ugyanakkor az SMP rendszereknek vannak hátrányai is. Az egyik fő kihívás a memória-hozzáférés szinkronizálása. Mivel minden processzor ugyanahhoz a memóriához fér hozzá, biztosítani kell, hogy a különböző processzorok által végzett memória-műveletek ne ütközzenek. Ez bonyolult szinkronizációs mechanizmusokat igényel, ami növelheti a rendszer komplexitását és csökkentheti a teljesítményt.

Egy másik hátrány a skálázhatóság korlátai. Ahogy a processzorok száma nő, a memória-hozzáférés szinkronizációjának költségei is növekednek, ami végül korlátozza a rendszer skálázhatóságát. Ezenkívül az SMP rendszerek drágábbak lehetnek, mint az egyprocesszoros rendszerek, mivel több processzort és komplexebb alaplapot igényelnek. A programozás szempontjából is nagyobb kihívást jelenthet az SMP rendszerekhez optimalizált szoftverek fejlesztése, mivel a párhuzamosítás és a szinkronizáció speciális ismereteket igényel.

Összességében az SMP rendszerek jelentős előnyöket kínálnak a párhuzamos feldolgozás terén, de a tervezésük és a használatuk során figyelembe kell venni a felmerülő kihívásokat is. A megfelelő alkalmazások esetén azonban jelentősen javíthatják a rendszer teljesítményét és megbízhatóságát.

Az SMP hardverkomponenseinek részletes elemzése: processzorok, memória, buszrendszer

A szimmetrikus többprocesszoros feldolgozás (SMP) lényege, hogy több processzor osztozik egy közös memóriaterületen, lehetővé téve a párhuzamos feladatvégzést. Az SMP rendszerek hatékonysága nagymértékben függ a hardverkomponensek – processzorok, memória és buszrendszer – optimalizációjától.

A processzorok az SMP rendszer szívei. Mindegyik processzor rendelkezik saját gyorsítótárral (cache), ami a gyakran használt adatok és utasítások tárolására szolgál. A cache koherencia kulcsfontosságú az SMP rendszerekben. Ez biztosítja, hogy minden processzor a legfrissebb adatokkal dolgozzon, még akkor is, ha egy másik processzor módosította azokat. Két fő cache koherencia protokoll létezik: a snooping és a directory-based protokollok. A snooping protokollban minden processzor figyeli a buszon zajló adatátvitelt, míg a directory-based protokollban egy központi könyvtár tartja nyilván, hogy melyik processzor rendelkezik az adatok másolatával.

A memória az SMP rendszerekben közös hozzáférésű. Ez azt jelenti, hogy minden processzor közvetlenül elérheti a teljes memóriaterületet. A memória hozzáférés sebessége kritikus fontosságú, mivel a processzoroknak gyakran kell adatokat olvasniuk és írniuk a memóriába. A memória sávszélességének szűk keresztmetszete jelentősen befolyásolhatja a rendszer teljesítményét. A NUMA (Non-Uniform Memory Access) architektúra egy alternatív megoldás, amelyben a memória elosztott, és egyes processzorok gyorsabban érhetik el a saját lokális memóriájukat, mint a többi processzor memóriáját. Ez csökkentheti a memória hozzáférési késleltetést, de bonyolultabb programozást igényel.

A buszrendszer az a kommunikációs csatorna, amely összeköti a processzorokat, a memóriát és az I/O eszközöket. A buszrendszer sávszélessége meghatározza, hogy mennyi adatot lehet egyszerre átvinni a különböző komponensek között. A gyors és hatékony buszrendszer elengedhetetlen az SMP rendszerek optimális működéséhez. A buszrendszerek lehetnek központi busz alapúak vagy kapcsolati hálózat alapúak. A központi busz alapú rendszerekben minden komponens egy közös buszra csatlakozik, míg a kapcsolati hálózat alapú rendszerekben a komponensek pont-pont kapcsolatokkal kapcsolódnak egymáshoz, ami nagyobb sávszélességet és skálázhatóságot tesz lehetővé. A buszrendszernek kezelnie kell a busz versengést is, amikor több processzor próbál egyszerre hozzáférni a buszhoz. Ezt általában valamilyen arbitrációs mechanizmussal oldják meg.

Az SMP rendszerek teljesítménye a processzorok számának növelésével elméletileg javul, azonban a valóságban a cache koherencia fenntartásának és a buszrendszer korlátainak köszönhetően a teljesítmény növekedése csökkenő mértékűvé válik.

A cache koherencia problémája SMP rendszerekben és a megoldási módszerek

A szimmetrikus többprocesszoros (SMP) rendszerekben, ahol több processzor osztozik a memórián, a cache koherencia problémája kritikus fontosságúvá válik. Ez a probléma akkor merül fel, amikor több processzor is rendelkezik egy adott memóriacellának a másolatával a saját cache-ében.

Tegyük fel, hogy egy processzor módosítja a cache-ében tárolt adatot. Ebben az esetben a többi processzor cache-ében lévő, azonos adatot tartalmazó másolatok elavulttá válnak. Ha ezek a processzorok ezután a saját cache-ükből olvassák az adatot, akkor hibás eredményt kapnak. A cache koherencia biztosítja, hogy minden processzor mindig a legfrissebb, helyes adatot használja, függetlenül attól, hogy melyik cache-ben tárolódik.

Számos módszer létezik a cache koherencia problémájának megoldására. A leggyakoribbak a snooping protokollok és a directory-alapú protokollok.

A snooping protokollok esetében minden processzor figyeli (snoop) a memóriabuszt, hogy észlelje a más processzorok által végzett memóriaműveleteket. Amikor egy processzor ír egy memóriacellába, a többi processzor, amelynek a cache-ében az adott cella másolata megtalálható, érvényteleníti a saját másolatát, vagy frissíti azt az új értékkel. Erre példa a MESI protokoll (Modified, Exclusive, Shared, Invalid), ami a legtöbb mai processzorban megtalálható.

A snooping protokollok előnye, hogy egyszerűen implementálhatók és alacsony a késleltetésük. Hátrányuk viszont, hogy a memóriabusznak nagy sávszélességre van szüksége, ami skálázási problémákat okozhat nagyobb processzorszám esetén.

A directory-alapú protokollok egy központi könyvtárat (directory) használnak, amely nyomon követi, hogy melyik cache-ben található meg egy adott memóriacella másolata. Amikor egy processzor ír egy memóriacellába, a rendszer lekérdezi a könyvtárat, hogy megtudja, mely processzorok rendelkeznek a cella másolatával. A könyvtár ezután üzenetet küld ezeknek a processzoroknak, hogy érvénytelenítsék vagy frissítsék a cache-üket.

A directory-alapú protokollok előnye, hogy jobban skálázhatók, mint a snooping protokollok, mivel nem igénylik a memóriabusz állandó figyelését. Hátrányuk viszont, hogy bonyolultabbak az implementálásuk és magasabb a késleltetésük.

A cache koherencia fenntartásának egyik gyakori módszere a write-invalidate protokoll. Ebben az esetben, amikor egy processzor ír a cache-ébe, a többi processzor cache-ében lévő másolatokat érvényteleníti. A másik lehetőség a write-update protokoll, ahol a módosításokat azonnal elküldik a többi cache-nek is.

A hamis megosztás (false sharing) egy másik probléma, ami SMP rendszerekben felmerülhet. Ez akkor fordul elő, amikor két processzor különböző adatokat módosít ugyanazon a cache-soron belül. Bár a processzorok valójában különböző adatokat módosítanak, a cache koherencia protokoll azt érzékeli, mintha ugyanazt az adatot módosítanák, ami felesleges cache érvénytelenítésekhez és adatmozgásokhoz vezet.

A megfelelő cache koherencia protokoll kiválasztása az adott rendszer követelményeitől függ. A kisebb rendszerekben a snooping protokollok elegendőek lehetnek, míg a nagyobb rendszerekben a directory-alapú protokollok nyújtanak jobb teljesítményt.

A szoftver szerepe az SMP rendszerekben: operációs rendszerek és alkalmazások

A szimmetrikus többprocesszoros (SMP) rendszerek hatékony működése nagymértékben függ a szoftveres támogatástól. Az operációs rendszerek (OS) és az alkalmazások kulcsszerepet játszanak abban, hogy az SMP architektúra előnyeit ki lehessen aknázni.

Az operációs rendszer feladata, hogy elosztja a feladatokat a rendelkezésre álló processzorok között. Egy SMP-re optimalizált OS képes párhuzamosan futtatni több szálat (thread) vagy folyamatot (process), így a rendszer összteljesítménye jelentősen javul. A modern operációs rendszerek, mint például a Linux, Windows Server és macOS, alapvetően támogatják az SMP-t. Ezen rendszerek ütemezési algoritmusai arra törekednek, hogy a processzorok kihasználtsága egyenletes legyen, és a feladatok a lehető leggyorsabban végrehajtódjanak.

Az OS felelős továbbá a szinkronizációért és a kommunikációért a processzorok között. Mivel több processzor egyszerre férhet hozzá a memóriához és más erőforrásokhoz, elengedhetetlen, hogy az OS biztosítsa az adatok konzisztenciáját és elkerülje a versenyhelyzeteket (race condition). Ehhez különböző szinkronizációs mechanizmusokat alkalmaznak, például zárakat (locks), szemaforokat (semaphores) és monitorokat.

Az alkalmazások szempontjából az SMP-támogatás azt jelenti, hogy képesek párhuzamosan végrehajtani feladatokat. Ezt többféleképpen lehet elérni:

- Szálak (threads) használata: Az alkalmazás több szálat hoz létre, amelyek párhuzamosan futnak a különböző processzorokon. Ez a módszer különösen hatékony számításigényes feladatok esetén.

- Folyamatok (processes) használata: Az alkalmazás több folyamatot indít el, amelyek egymástól függetlenül futnak. Ez a módszer alkalmas olyan feladatok párhuzamosítására, amelyek nem osztoznak közös memórián.

- Párhuzamos könyvtárak és keretrendszerek használata: Számos könyvtár és keretrendszer létezik, amelyek megkönnyítik a párhuzamos alkalmazások fejlesztését. Ilyen például az OpenMP, a MPI (Message Passing Interface) és a CUDA (NVIDIA).

Egy alkalmazás akkor tudja maximálisan kihasználni az SMP előnyeit, ha a feladatok jól párhuzamosíthatók, és a processzorok közötti kommunikáció minimálisra csökkenthető.

Nem minden alkalmazás profitál egyformán az SMP-ből. Azok az alkalmazások, amelyek nagymértékben függenek a szekvenciális kódtól, vagy amelyekben sok az adatfüggőség, kevésbé tudják kihasználni a többprocesszoros architektúrát. Az Amdahl törvénye kimondja, hogy a program párhuzamosításával elérhető maximális gyorsulás korlátozott, és függ a szekvenciális rész arányától.

A szoftverfejlesztőknek tehát gondosan meg kell tervezniük az alkalmazásokat, hogy azok hatékonyan tudják kihasználni az SMP rendszerekben rejlő lehetőségeket. Ez magában foglalja a megfelelő párhuzamosítási stratégia kiválasztását, a szinkronizációs mechanizmusok helyes használatát, és az adatok hatékony elosztását a processzorok között.

Az SMP operációs rendszerek feladatai: szálkezelés, ütemezés, szinkronizáció

A szimmetrikus többprocesszoros (SMP) rendszerekben az operációs rendszer kulcsszerepet játszik a rendelkezésre álló processzorok hatékony kihasználásában. Ennek alapvető elemei a szálkezelés, az ütemezés és a szinkronizáció.

A szálkezelés feladata a programok futásához szükséges szálak létrehozása, kezelése és megszüntetése. Egyetlen program több szálra bontható, amelyek párhuzamosan futhatnak a különböző processzorokon. Az operációs rendszernek biztosítania kell, hogy ezek a szálak hatékonyan és biztonságosan használják a rendszert.

Az ütemezés az a folyamat, amely során az operációs rendszer eldönti, hogy melyik szál fusson melyik processzoron, és mennyi ideig. Az SMP rendszerekben az ütemező célja, hogy a terhelést egyenletesen ossza el a processzorok között, minimalizálva az üresjáratot és maximalizálva a rendszer teljesítményét. Ehhez gyakran használnak olyan algoritmusokat, amelyek figyelembe veszik a szálak prioritását és a processzorok terheltségét.

A szinkronizáció elengedhetetlen a párhuzamosan futó szálak közötti helyes adatkezeléshez. Több szál is hozzáférhet ugyanahhoz a memóriaterülethez, és ha nem megfelelően szinkronizálják a hozzáférést, az adatok sérüléséhez vagy inkonzisztens állapotokhoz vezethet. Az operációs rendszer különféle szinkronizációs mechanizmusokat biztosít, például mutexeket, szemaforokat és kritikus szakaszokat, amelyek lehetővé teszik a szálak számára, hogy biztonságosan osszák meg az erőforrásokat.

Az SMP rendszerek hatékonysága nagymértékben függ az operációs rendszer képességétől, hogy megfelelően kezelje a szálakat, ütemezze a futtatásukat és szinkronizálja a hozzáférésüket a közös erőforrásokhoz.

Az operációs rendszernek emellett kezelnie kell az affinitást is, ami azt jelenti, hogy bizonyos szálakat preferált processzorokhoz rendelhet. Ez javíthatja a teljesítményt, mivel a szálak kevésbé valószínű, hogy át kelljen helyezni őket a processzorok között, ami időigényes művelet.

Továbbá, az operációs rendszernek képesnek kell lennie a skálázhatóság biztosítására is. Ahogy a rendszerbe több processzor kerül, az operációs rendszernek képesnek kell lennie a terhelés egyenletes elosztására és a szinkronizációs problémák kezelésére anélkül, hogy a teljesítmény jelentősen romlana.

A szálkezelés és a szinkronizáció kihívásai SMP környezetben: holtpontok, versengési feltételek

A szimmetrikus többprocesszoros (SMP) rendszerekben, ahol több processzor osztozik a memórián és az I/O eszközökön, a szálkezelés és a szinkronizáció kritikus fontosságúvá válik. A párhuzamos végrehajtás előnyeinek kihasználása komoly kihívásokat is rejt magában, különösen a holtpontok (deadlocks) és a versengési feltételek (race conditions) elkerülése terén.

A holtpont egy olyan helyzet, amikor két vagy több szál örökké várakozik egymásra, mert mindegyikük egy olyan erőforrást tart, amelyre a másiknak szüksége van. Ez egy ördögi körhöz vezet, amelyben egyik szál sem tudja folytatni a munkáját. Képzeljük el, hogy két szál próbál hozzáférni két különböző erőforráshoz (A és B). Az egyik szál lefoglalja A-t, a másik B-t. Ezután az első szál próbálja lefoglalni B-t, miközben a második szál A-ra vár. Ekkor mindkét szál várakozik, és a rendszer „befagy”.

A holtpont elkerülése érdekében a szálkezelés során figyelmet kell fordítani az erőforrás-foglalás sorrendjére, és kerülni kell a körkörös függőségeket.

A versengési feltétel akkor lép fel, amikor több szál ugyanahhoz a megosztott adathoz próbál hozzáférni és azt módosítani, és a végeredmény a szálak végrehajtási sorrendjétől függ. Ez az adatok inkonzisztenciájához és hibás működéshez vezethet. Például, ha két szál egyszerre próbálja növelni egy közös változó értékét, akkor a végeredmény nem feltétlenül lesz a várt érték, mert a szálak egymás műveleteit felülírhatják.

A versengési feltételek kezelésére különböző szinkronizációs mechanizmusok állnak rendelkezésre, mint például a mutexek (kizárólagos zárak), a szemafórok és a kritikus szakaszok. A mutex lehetővé teszi, hogy egyszerre csak egy szál férjen hozzá egy adott erőforráshoz vagy adathoz. A szemafórok ennél általánosabbak, és lehetővé teszik, hogy egy adott számú szál egyszerre férjen hozzá egy erőforráshoz. A kritikus szakaszok olyan kódrészek, amelyek csak egy szál által hajthatók végre egyszerre.

A szinkronizáció helyes használata elengedhetetlen az SMP rendszerekben a szálak közötti koordináció biztosításához és az adatok integritásának megőrzéséhez. A szinkronizációs mechanizmusok túlzott vagy helytelen használata azonban teljesítményproblémákhoz, például száléheztetéshez (thread starvation) vezethet, amikor egy szál hosszú ideig nem jut hozzá a szükséges erőforrásokhoz, vagy prioritás inverzióhoz (priority inversion), amikor egy alacsonyabb prioritású szál blokkol egy magasabb prioritású szálat.

A hatékony szálkezelés és szinkronizáció megvalósítása az SMP rendszerekben gondos tervezést és tesztelést igényel. A fejlesztőknek alaposan meg kell érteniük a szálak közötti kölcsönhatásokat, és a megfelelő szinkronizációs mechanizmusokat kell alkalmazniuk a holtpontok és a versengési feltételek elkerülése érdekében. Emellett figyelembe kell venniük a szinkronizáció teljesítményre gyakorolt hatását, és a lehető legkisebbre kell csökkenteniük a zárak (locks) használatát, hogy maximalizálják a párhuzamos végrehajtás előnyeit.

- Holtpont elkerülése: Erőforrás-foglalás sorrendjének szabályozása, körkörös függőségek kerülése.

- Versengési feltételek kezelése: Mutexek, szemafórok, kritikus szakaszok használata.

- Szinkronizációs problémák: Száléheztetés, prioritás inverzió.

Az SMP rendszerek teljesítményének optimalizálása: terheléselosztás, adatok lokalitása

Az SMP rendszerek teljesítményének optimalizálása kulcsfontosságú a hatékony párhuzamos feldolgozás eléréséhez. Két fő területre kell fókuszálni: a terheléselosztásra és az adatok lokalitására.

A terheléselosztás célja, hogy a munkát egyenletesen ossza el a processzorok között. Ha egy processzor túlterhelt, míg a többi tétlen, az jelentősen rontja a teljesítményt. Két fő terheléselosztási stratégia létezik:

- Statikus terheléselosztás: A feladatokat a program futása előtt osztjuk el a processzorok között. Ez egyszerű, de nem optimális, ha a feladatok futási ideje változó.

- Dinamikus terheléselosztás: A feladatokat a program futása közben osztjuk el, figyelembe véve a processzorok aktuális terhelését. Ez rugalmasabb, de többletterhelést okoz a feladatok elosztása.

A jó terheléselosztás elengedhetetlen, de önmagában nem elegendő a maximális teljesítményhez. Az adatok lokalitása is kritikus tényező. A processzorok gyorsabban hozzáférnek a saját helyi memóriájukhoz (cache), mint a távoli memóriához. Ha a processzorok gyakran kényszerülnek távoli memóriából adatokat beolvasni, az úgynevezett cache miss-ekhez vezet, ami jelentősen lassítja a feldolgozást.

A cél az, hogy a processzorok a lehető legtöbb adatot a saját cache-ükben tárolják, minimalizálva a memóriahozzáférési késleltetést.

Az adatok lokalitásának javítására számos technika létezik:

- Adatok particionálása: Az adatokat úgy osztjuk fel a processzorok között, hogy minden processzor a saját partíciójával foglalkozzon.

- Adatok replikálása: A gyakran használt adatokat több processzor is tárolja a saját cache-ében.

- Szálak affinitása: A szálakat olyan processzorokhoz rendeljük, amelyek már rendelkeznek a szükséges adatokkal a cache-ükben.

A terheléselosztás és az adatok lokalitása közötti egyensúly megtalálása komplex feladat. A legjobb megoldás nagymértékben függ az adott alkalmazástól és a hardverarchitektúrától. A hatékony SMP rendszerek tervezése során mindkét tényezőt figyelembe kell venni annak érdekében, hogy a párhuzamos feldolgozás előnyeit maximálisan ki lehessen aknázni.

A szálak helyes kezelése is fontos tényező. A túl sok szál létrehozása overhead-et okozhat (pl. kontextusváltás), míg a túl kevés szál nem használja ki megfelelően a rendelkezésre álló processzorokat.

Az SMP rendszerek hibatűrése és megbízhatósága

Az SMP rendszerek egyik legfontosabb előnye a fokozott hibatűrés és megbízhatóság. Mivel több processzor dolgozik párhuzamosan, egy processzor meghibásodása esetén a rendszer nem áll le teljesen. Ehelyett a többi processzor átveheti a kiesett processzor feladatait, így a rendszer folyamatosan, bár esetleg csökkentett teljesítménnyel tovább tud működni.

Ez a redundancia kritikus fontosságú lehet olyan alkalmazásokban, ahol a folyamatos működés elengedhetetlen, például szerverfarmok, pénzügyi rendszerek vagy orvosi berendezések esetében.

Az SMP architektúra lehetővé teszi a rendszer számára, hogy a hardveres hibák ellenére is működőképes maradjon, minimalizálva a kiesési időt és a potenciális adatvesztést.

A hibatűrés mértéke természetesen függ a rendszer felépítésétől és a futó alkalmazások kritikus fontosságától. Bizonyos esetekben a rendszer automatikusan képes átcsoportosítani a feladatokat, míg más esetekben manuális beavatkozás szükséges lehet.

A megbízhatóság növelése érdekében az SMP rendszerek gyakran rendelkeznek redundáns tápegységekkel, hűtőrendszerekkel és memóriával is. Ezek az intézkedések tovább csökkentik a rendszer meghibásodásának kockázatát.

A megfelelő monitoring és hibaelhárítási eljárások szintén elengedhetetlenek az SMP rendszerek megbízhatóságának fenntartásához. A rendszeres ellenőrzések és a gyors reagálás a felmerülő problémákra segíthetnek megelőzni a komolyabb problémákat és biztosítani a rendszer folyamatos működését.

Az SMP alkalmazási területei: szerverek, munkaállomások, speciális rendszerek

A szimmetrikus többprocesszoros feldolgozás (SMP) technológiát széles körben alkalmazzák különböző számítástechnikai területeken, kihasználva a párhuzamos feldolgozás előnyeit. A szerverek esetében az SMP elengedhetetlen a nagy terhelés kezeléséhez, a többfelhasználós környezetek kiszolgálásához és az adatbázis-kezeléshez. Minél több processzor áll rendelkezésre, annál több kérést tud egyidejűleg kezelni a szerver, ezáltal javítva a válaszidőt és a felhasználói élményt.

A munkaállomások területén az SMP különösen hasznos a számításigényes feladatokhoz, mint például a videószerkesztés, a 3D modellezés és a tudományos szimulációk. A több processzor lehetővé teszi a komplex számítások gyorsabb elvégzését, ami jelentősen csökkenti a munkafolyamatok időtartamát. A grafikusok, mérnökök és tudósok számára ez a teljesítménybeli előny kritikus fontosságú.

Végül, az SMP-t speciális rendszerekben is alkalmazzák, például a nagy teljesítményű számítástechnikai (HPC) klaszterekben, az orvosi képalkotó rendszerekben és a valós idejű rendszerekben. A HPC klaszterekben az SMP lehetővé teszi a rendkívül komplex problémák párhuzamos megoldását, míg az orvosi képalkotó rendszerekben a részletes képek gyors feldolgozását teszi lehetővé. A valós idejű rendszerekben, mint például az autonóm járművekben, az SMP biztosítja a szenzoradatok gyors és megbízható feldolgozását, ami elengedhetetlen a biztonságos működéshez.

Az SMP kulcsfontosságú szerepet játszik a modern számítástechnikai rendszerek teljesítményének növelésében és a komplex feladatok hatékony elvégzésében.

Az SMP alkalmazásának köszönhetően a különböző rendszerek képesek hatékonyabban kezelni a növekvő számítási igényeket, és jobb teljesítményt nyújtani a felhasználóknak.

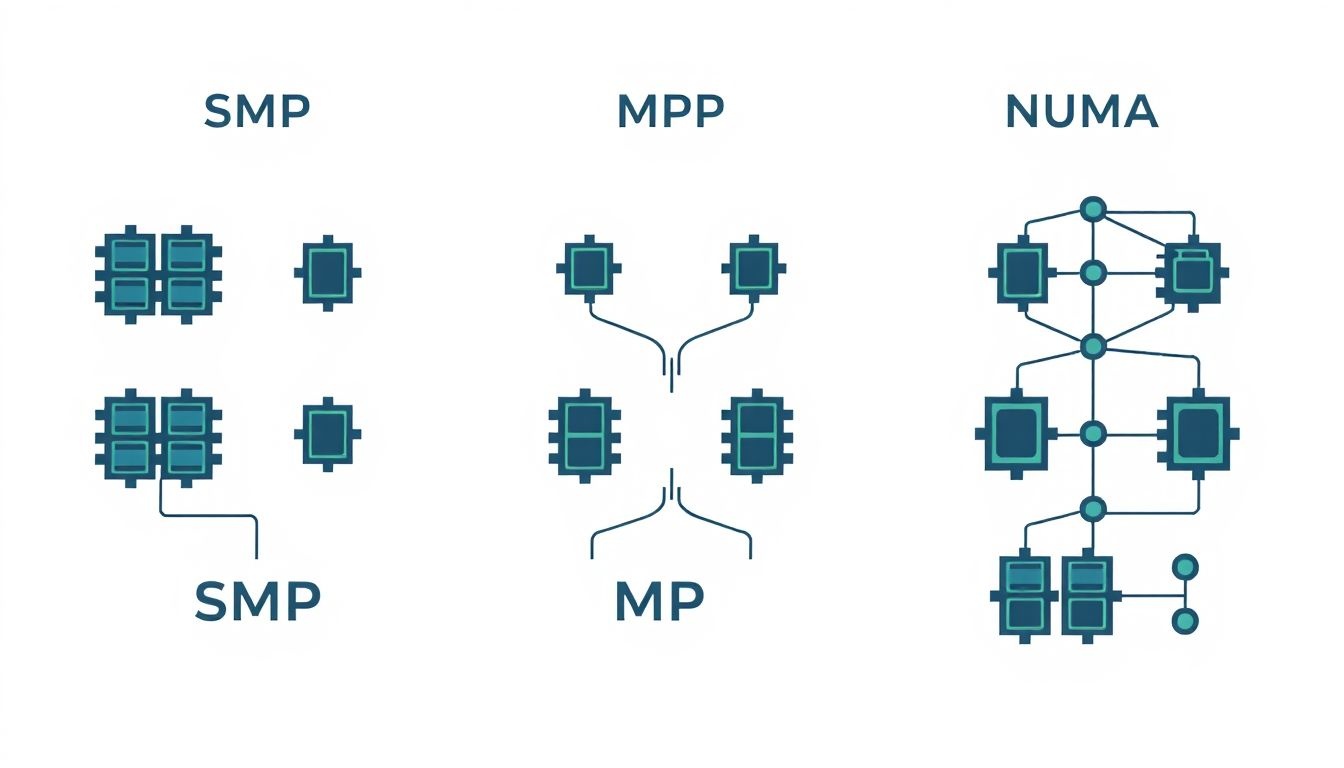

Az SMP és más párhuzamos feldolgozási architektúrák összehasonlítása: MPP, NUMA

A szimmetrikus többprocesszoros feldolgozás (SMP) egy olyan architektúra, ahol több processzor osztozik ugyanazon a közös memórián és I/O buszon. Ezzel szemben állnak más párhuzamos feldolgozási modellek, amelyek eltérő megközelítéseket alkalmaznak.

A Massively Parallel Processing (MPP) rendszerekben sok processzor található, amelyek mindegyike saját dedikált memóriával és I/O alrendszerrel rendelkezik. A processzorok egy nagy sebességű összeköttetésen keresztül kommunikálnak egymással. Az MPP rendszerek nagyon jól skálázhatók, és alkalmasak nagy mennyiségű adat párhuzamos feldolgozására, de a programozásuk bonyolultabb lehet, mint az SMP rendszereké, mivel a fejlesztőknek explicit módon kell kezelniük a processzorok közötti adatátvitelt.

A Non-Uniform Memory Access (NUMA) architektúra egy hibrid megoldás, amely az SMP és az MPP előnyeit igyekszik ötvözni. A NUMA rendszerekben a processzorok csoportokba vannak szervezve, és minden csoportnak van egy helyi memóriája. A processzorok gyorsabban érik el a helyi memóriát, mint a távoli memóriát, ami befolyásolja a teljesítményt. A NUMA célja, hogy a közös memória egyszerűségét megőrizze, miközben lehetővé teszi a skálázhatóságot és a helyi memória gyors elérését. A NUMA rendszerek programozása bonyolult lehet, mivel a fejlesztőknek figyelembe kell venniük a memória elérésének költségeit.

Az SMP rendszerek a legkönnyebben programozhatók, de a skálázhatóságuk korlátozott. Az MPP rendszerek a legjobban skálázhatók, de a programozásuk a legbonyolultabb. A NUMA rendszerek egy kompromisszumot jelentenek a kettő között.

Az SMP rendszerekben a cache koherencia kritikus fontosságú. Mivel minden processzor ugyanazt a memóriát használja, biztosítani kell, hogy a processzorok cache-ében tárolt adatok konzisztensek maradjanak. Ezt különböző protokollok biztosítják, mint például a snooping protokoll vagy a directory-based protokoll.

Összefoglalva, az SMP, MPP és NUMA architektúrák különböző kompromisszumokat kínálnak a teljesítmény, a skálázhatóság és a programozási bonyolultság terén. A megfelelő architektúra kiválasztása a konkrét alkalmazás követelményeitől függ.