A modern számítástechnika alapköve a processzor, melynek minden egyes művelete egy rendkívül komplex és precíz koreográfia eredménye. Ennek a koreográfiának a karmestere a vezérlőegység (Control Unit, CU), a CPU azon része, amely felelős az utasítások értelmezéséért, a végrehajtásukhoz szükséges jelek generálásáért, és a processzor többi komponensének összehangolt működéséért. Nélküle a processzor csupán egy halott szilíciumdarab lenne, képtelen bármilyen értelmes feladat elvégzésére. Ez a cikk a vezérlőegység mélyebb rétegeibe kalauzol el bennünket, feltárva működésének alapelveit, architekturális megvalósításait és kulcsfontosságú szerepét a számítástechnika világában.

A processzor, vagyis a központi feldolgozóegység (Central Processing Unit – CPU), számos komponenst foglal magában, mint például az aritmetikai-logikai egység (ALU), a regiszterek és a gyorsítótár. Ezek mindegyike speciális feladatot lát el, de ahhoz, hogy együtt, szinkronban dolgozzanak, szükség van egy központi irányítóra. Ezt a szerepet tölti be a vezérlőegység, amely nem csupán a processzoron belüli adatfolyamot és műveleteket koordinálja, hanem a CPU és a külső memória, valamint a perifériák közötti kommunikációt is felügyeli. Ez a láthatatlan, mégis elengedhetetlen komponens biztosítja, hogy a szoftveres utasítások hardveres műveletekké alakuljanak, és a számítógép pontosan azt tegye, amit elvárunk tőle.

A vezérlőegység működésének megértése kulcsfontosságú ahhoz, hogy átfogó képet kapjunk a processzorok működéséről és a számítógépes rendszerek alapjairól. A digitális elektronika és a logikai kapuk szintjétől egészen a komplex utasításkészletek kezeléséig terjedő feladatköre teszi igazán érdekessé és tanulmányozásra méltóvá. Fedezzük fel együtt, hogyan kel életre a szilícium, és hogyan válik a vezérlőegység a modern technológia egyik legfontosabb alkotóelemévé.

A vezérlőegység történelmi áttekintése és fejlődése

A vezérlőegység koncepciója már a számítógépek hajnalán megjelent, amikor Neumann János és munkatársai lefektették a tárolt programú számítógépek alapjait. Az első gépekben a vezérlés még viszonylag egyszerű volt, de ahogy a processzorok egyre összetettebbé váltak, úgy nőtt a vezérlőegységek bonyolultsága és jelentősége is. Kezdetben a vezérlő logika szinte teljes egészében hardveresen volt huzalozva, ami azt jelentette, hogy minden egyes utasítás végrehajtásához szükséges vezérlőjel-sorozatot fizikai áramkörök valósítottak meg. Ez a megközelítés gyors volt, de rendkívül rugalmatlan.

A mikrokódos vezérlés megjelenése az 1950-es évek végén forradalmasította a vezérlőegységek tervezését. Maurice Wilkes és J. R. Stringer nevéhez fűződik ez az innováció, amely lehetővé tette, hogy a komplex utasítások végrehajtásához szükséges vezérlőjel-sorozatokat egy speciális, belső, olvasható memória (Control Store) tárolja. Ez a megközelítés sokkal rugalmasabbá tette a processzorok tervezését, mivel az utasításkészlet változtatásai vagy bővítései egyszerűen a mikrokód frissítésével valósíthatók meg, anélkül, hogy a fizikai áramköröket módosítani kellene. A mikrokódos vezérlés különösen a CISC (Complex Instruction Set Computer) architektúrákban vált dominánssá, ahol az utasítások rendkívül összetettek lehetnek.

A RISC (Reduced Instruction Set Computer) architektúrák előretörése az 1980-as években újabb fordulatot hozott. A RISC processzorok az egyszerűbb, fix hosszúságú utasításkészletre fókuszáltak, ami lehetővé tette a vezérlőegységek ismételt hardveres huzalozását. Az egyszerűbb utasításokhoz kevesebb vezérlőjelre van szükség, és ezeket hatékonyabban lehet hardveresen implementálni. Ez a megközelítés rendkívül gyors végrehajtást biztosított, mivel nem volt szükség a mikrokód értelmezésére. A modern processzorok gyakran hibrid megoldásokat alkalmaznak, ahol a kritikus, gyakran használt utasítások hardveresen vannak vezérelve, míg a ritkább, komplexebb utasítások mikrokódot használnak.

Az elmúlt évtizedekben a vezérlőegységek fejlődését a sebesség, az energiahatékonyság és a komplexitás növekedése jellemezte. A pipelining, a branch prediction (elágazás-előrejelzés) és az out-of-order execution (sorrenden kívüli végrehajtás) technikák bevezetése mind a vezérlőegység intelligenciájának és összetettségének növekedését igényelte. Ezek a technikák lehetővé teszik a processzor számára, hogy párhuzamosan több utasítást dolgozzon fel, kihasználva a rendelkezésre álló erőforrásokat és maximalizálva a teljesítményt. A mai vezérlőegységek sokkal kifinomultabbak, mint elődeik, képesek dinamikusan alkalmazkodni a programok igényeihez és optimalizálni a végrehajtást.

A vezérlőegység alapvető feladatai és funkciói

A vezérlőegység, mint a processzor központi agya, számos kritikus feladatot lát el, amelyek nélkül a CPU nem lenne képes működni. Ezek a feladatok a programutasítások legelejétől a végrehajtásukig tartó teljes ciklust lefedik, biztosítva a zökkenőmentes és pontos működést. A legfontosabb funkciók közé tartozik az utasításlehívás, az utasításdekódolás, a végrehajtás koordinálása és az eredmények visszaírása.

Az első és talán legfontosabb feladata az utasításlehívás (Instruction Fetch). A vezérlőegység felelős azért, hogy a programszámláló (Program Counter, PC) regiszterben tárolt címről lekérje a következő végrehajtandó utasítást a memóriából. Ezt az utasítást az utasításregiszterbe (Instruction Register, IR) tölti be, ahol az további feldolgozásra vár. Ez a lépés biztosítja, hogy a processzor mindig tudja, mi a következő teendője, és fenntartja a program futásának folytonosságát.

Miután az utasítás bekerült az IR-be, következik az utasításdekódolás (Instruction Decode). Ebben a fázisban a vezérlőegység elemzi az utasítást, hogy meghatározza annak típusát, az operandusok számát és helyét, valamint a végrehajtandó műveletet. Ez a dekódolás történhet hardveresen, logikai áramkörök segítségével, vagy mikrokódos vezérlés esetén egy belső, speciális memóriából kiolvasott mikrokód-sorozat segítségével. A dekódolás eredményeként a vezérlőegység pontosan tudja, milyen vezérlőjeleket kell generálnia a következő fázisban.

A dekódolás után a vezérlőegység feladata a végrehajtás koordinálása (Execute). Ez magában foglalja az összes szükséges vezérlőjel generálását, amelyek a processzor különböző részeinek aktiválásához szükségesek. Például, ha az utasítás egy összeadást ír elő, a CU jeleket küld az aritmetikai-logikai egységnek (ALU), hogy hajtsa végre az összeadást, aktiválja a megfelelő regisztereket az operandusokhoz, és irányítja az eredmény tárolását. Ezen felül a CU kezeli a memóriahozzáférést is, ha az utasítás adatokat olvasna vagy írna a memóriába.

A vezérlőegység a processzor nem látható karmestere, mely minden egyes taktusciklusban milliónyi döntést hoz, hogy a szoftveres utasítások precízen és hatékonyan valósuljanak meg a hardveren keresztül.

Végül, de nem utolsósorban, a vezérlőegység felügyeli az eredmények visszaírását (Write-Back). Miután egy műveletet az ALU végrehajtott, vagy adatot olvastunk a memóriából, az eredményt vissza kell írni egy regiszterbe vagy a memóriába. A CU biztosítja, hogy ez a visszaírás a megfelelő helyre és a megfelelő időben történjen. Emellett a vezérlőegység felelős az órajel (Clock Signal) szinkronizálásáért is, biztosítva, hogy minden művelet a megfelelő taktusciklusban történjen, és a processzor komponensei harmonikusan működjenek együtt.

Összességében a vezérlőegység feladatai rendkívül szerteágazóak és komplexek. Nem csupán utasításokat dekódol, hanem folyamatosan felügyeli a processzor állapotát, kezeli a megszakításokat, és biztosítja a program zökkenőmentes futását. Ez a sokoldalú szerep teszi a vezérlőegységet a processzor egyik legfontosabb és legmeghatározóbb komponensévé.

A vezérlőegység architektúrája: Hardveres és mikrokódos megvalósítások

A vezérlőegység belső felépítése alapvetően két fő kategóriába sorolható: hardveres huzalozású (hardwired) és mikrokódos (microprogrammed) megvalósítások. Mindkét megközelítésnek megvannak a maga előnyei és hátrányai, és az alkalmazásuk nagymértékben függ a processzor architektúrájától és tervezési filozófiájától.

Hardveres huzalozású vezérlőegység

A hardveres huzalozású vezérlőegység logikai kapuk, flip-flopok és kombinációs áramkörök komplex hálózatából épül fel. Ebben a megközelítésben minden egyes utasításhoz tartozó vezérlőjel-sorozatot közvetlenül fizikai áramkörök generálnak. Amikor egy utasítás dekódolásra kerül, a dekóder kimenete aktiválja a megfelelő logikai áramkört, amely aztán a szükséges időzítéssel és sorrendben előállítja a vezérlőjeleket a processzor többi egységének. Ez a megoldás gyakran alkalmazott a RISC (Reduced Instruction Set Computer) architektúrákban, ahol az utasításkészlet egyszerűbb és fix hosszúságú, így a vezérlő logika is egyszerűsíthető.

A hardveres vezérlés legnagyobb előnye a sebesség. Mivel nincsen szükség mikrokódos memória olvasására és értelmezésére, a vezérlőjelek generálása rendkívül gyorsan történik. Ez ideálissá teszi az olyan alkalmazásokhoz, ahol a maximális teljesítmény kritikus. Azonban van hátránya is: a rugalmatlanság. Ha az utasításkészletet módosítani vagy bővíteni kell, vagy egy hibát javítani, az a fizikai áramkörök áttervezését és újragyártását igényli, ami költséges és időigényes folyamat. Emellett, minél komplexebb az utasításkészlet, annál bonyolultabbá és nagyobbá válik a hardveres vezérlőegység, ami növeli a chip méretét és az energiafogyasztást.

Mikrokódos vezérlőegység

A mikrokódos vezérlőegység egy alternatív megközelítés, amely egy speciális, belső memóriát, az úgynevezett vezérlő tárat (Control Store) használja a vezérlőjelek tárolására. Minden egyes géputasítás egy vagy több mikroutasítás sorozatára bomlik, és ezek a mikroutasítások tárolódnak a vezérlő tárban. Amikor egy géputasítás dekódolásra kerül, a vezérlőegység megkeresi a hozzá tartozó mikrokód-sorozat kezdeti címét a vezérlő tárban, majd egymás után kiolvassa és végrehajtja a mikroutasításokat. Minden mikroutasítás közvetlenül generálja a szükséges vezérlőjeleket a processzor komponensei számára.

Ez a megközelítés különösen elterjedt a CISC (Complex Instruction Set Computer) architektúrákban, mint például az Intel x86 processzorok. A mikrokódos vezérlés egyik fő előnye a rugalmasság. Az utasításkészlet bővítése vagy módosítása egyszerűen a mikrokód frissítésével megoldható, akár a chip gyártása után is (például BIOS/UEFI frissítések részeként). Ez jelentősen leegyszerűsíti a tervezési és hibakeresési folyamatot. Ezen kívül a komplex utasítások implementálása is könnyebb, mivel a tervezőnek nem kell minden részletet hardveresen implementálnia.

| Jellemző | Hardveres huzalozású CU | Mikrokódos CU |

|---|---|---|

| Sebesség | Nagyon gyors | Lassabb (mikrokód olvasás miatt) |

| Rugalmasság | Alacsony (nehéz módosítani) | Magas (mikrokód frissíthető) |

| Komplexitás | Nő az utasításkészlettel | Viszonylag állandó (mikrokód mérete nő) |

| Tervezési idő | Hosszabb és bonyolultabb | Rövidebb és egyszerűbb |

| Alkalmazás | RISC processzorok | CISC processzorok |

| Példa | MIPS, SPARC | Intel x86, Motorola 68k |

A mikrokódos vezérlés hátránya a sebességcsökkenés. A mikrokód olvasása és értelmezése extra időt vesz igénybe, ami lassabb végrehajtást eredményezhet, mint a hardveresen vezérelt rendszerek esetében. Azonban a modern processzorok gyakran hibrid megoldásokat alkalmaznak, ahol a gyakran használt, egyszerű utasítások hardveresen vannak vezérelve, míg a ritkább, komplexebb utasítások mikrokódot használnak, kihasználva mindkét megközelítés előnyeit.

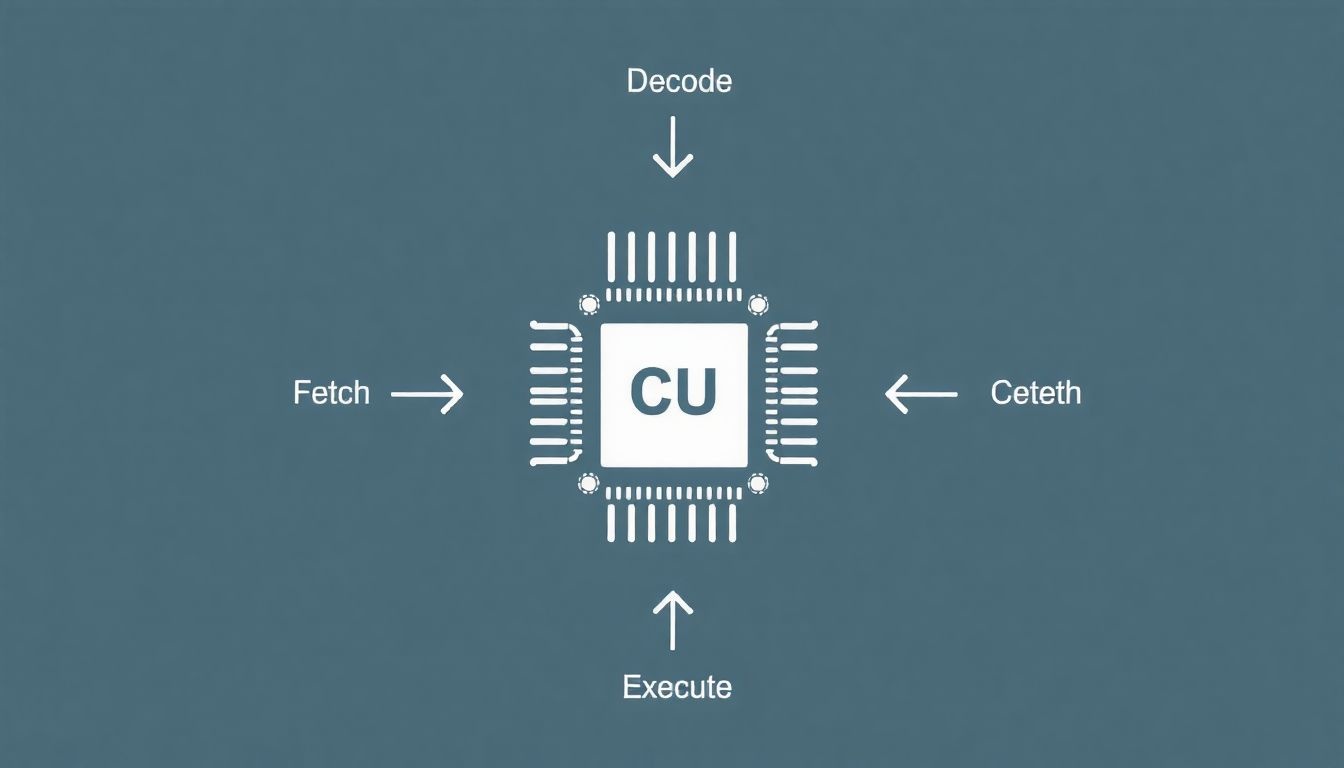

A vezérlőegység működési elve: Az utasításciklus

A processzor működésének alapja az utasításciklus (Instruction Cycle), más néven Fetch-Decode-Execute Cycle. Ez egy ismétlődő folyamat, amely során a CPU egy-egy programutasítást hajt végre. A vezérlőegység kulcsfontosságú szerepet játszik minden egyes fázisban, koordinálva az összes érintett komponenst. Négy fő fázisra bontható ez a ciklus: lehívás, dekódolás, végrehajtás és visszaírás.

1. Lehívás (Fetch)

A ciklus az utasítás lehívásával kezdődik. A programszámláló (PC) regiszter tartalmazza a következő végrehajtandó utasítás memóriacímét. A vezérlőegység ezt a címet elküldi a memóriacím-regiszternek (MAR), majd a MAR tartalmát a címbuszra helyezi. Ezt követően a vezérlőegység vezérlőjeleket generál a memóriának, hogy olvassa ki az adott címen található adatot. A memóriából kiolvasott utasítás a memória adatregiszterbe (MDR) kerül, majd onnan továbbítódik az utasításregiszterbe (IR). Ezzel egyidejűleg a vezérlőegység megnöveli a programszámláló tartalmát, hogy az a következő utasításra mutasson, felkészülve a következő ciklusra.

Ebben a fázisban a CU biztosítja az időzítést és a megfelelő jelzéseket a memória interfész számára. A cache memória is szerepet játszhat itt; ha az utasítás megtalálható a gyorsítótárban, akkor a lehívás sokkal gyorsabban történik, mint a főmemóriából. A CU felelős a cache-tal való interakció kezeléséért is, ellenőrizve, hogy az adat rendelkezésre áll-e a gyorsítótárban, és ha nem, akkor elindítva a főmemóriából történő betöltést.

2. Dekódolás (Decode)

Az utasításregiszterbe (IR) beérkezett utasítás most a dekódolás fázisába lép. A vezérlőegység elemzi az utasítás bináris kódját, hogy meghatározza annak típusát és a végrehajtandó műveletet. Ez a dekódolás feltárja, hogy az utasítás például egy aritmetikai művelet (összeadás, kivonás), egy logikai művelet (AND, OR), egy adatmozgatás (betöltés, tárolás) vagy egy vezérlőátadás (ugrás, elágazás). A dekódolás során a vezérlőegység azonosítja az utasításban szereplő operandusokat is, például, hogy azok regiszterekben, vagy memóriacímeken találhatók-e.

Az utasításciklus minden egyes lépése a vezérlőegység precíz irányítása alatt áll, ami biztosítja a program utasításainak hibátlan és szekvenciális végrehajtását.

A dekódolás eredményeként a vezérlőegység pontosan tudja, milyen vezérlőjeleket kell generálnia a következő fázisban, és melyik processzor komponenseket kell aktiválnia. Mikrokódos rendszerekben ez a fázis magában foglalja a géputasításhoz tartozó mikrokód-sorozat kezdeti címének megkeresését a vezérlő tárban.

3. Végrehajtás (Execute)

Ez a fázis a programutasítás tényleges végrehajtását jelenti. A vezérlőegység a dekódolt információk alapján generálja a szükséges vezérlőjeleket, amelyeket elküld a processzor releváns részeinek. Például, ha az utasítás egy összeadás, a CU aktiválja az aritmetikai-logikai egységet (ALU), beállítja az ALU funkcióját összeadásra, és elküldi az operandusokat tartalmazó regiszterek címeit vagy adatait az ALU-nak. Ha az utasítás memóriahozzáférést igényel, a CU vezérli a MAR és MDR regisztereket, valamint a memória interfészt az olvasási vagy írási művelet végrehajtásához.

A végrehajtás során a vezérlőegység felügyeli az összes érintett busz és regiszter tevékenységét, biztosítva az adatok megfelelő áramlását és az időzítés pontosságát. Ez a fázis a leginkább változatos, mivel az utasítás típusától függően nagyon eltérő műveleteket foglalhat magában.

4. Visszaírás (Write-Back)

Az utasításciklus utolsó fázisa az eredmények visszaírása. Miután a végrehajtás fázisában egy művelet befejeződött (pl. az ALU kiszámította az összeget), az eredményt vissza kell írni egy célregiszterbe vagy a memóriába. A vezérlőegység gondoskodik arról, hogy az eredmény a megfelelő helyre kerüljön. Például, ha az összeadás eredménye egy regiszterbe kerül, a CU aktiválja a megfelelő regisztert a beíráshoz. Ha az eredményt a memóriába kell írni, a CU vezérli a MAR és MDR regisztereket, valamint a memória interfészt az írási művelet végrehajtásához.

Ez a fázis biztosítja, hogy a program állapota frissüljön az éppen végrehajtott utasítás hatásainak megfelelően. A visszaírás után a vezérlőegység felkészül a következő utasításciklus megkezdésére, ismét a programszámlálóban található címről indulva.

Az utasításciklus folyamatosan ismétlődik, amíg a program be nem fejeződik, vagy egy megszakítási esemény nem állítja le. A vezérlőegység precíz irányítása elengedhetetlen a CPU stabil és megbízható működéséhez, hiszen minden egyes bit és minden egyes taktusciklus a vezérlőegység döntései alapján mozog a rendszerben.

Az utasításkészlet (Instruction Set Architecture – ISA) és a vezérlőegység kapcsolata

Az utasításkészlet architektúra (Instruction Set Architecture – ISA) egy alapvető interfész a szoftver és a hardver között, amely meghatározza azokat az utasításokat, amelyeket egy adott processzor képes végrehajtani. Az ISA lefekteti a processzor „nyelvtanát” és „szókincsét”, definiálva az utasítások formátumát, az operandusok típusait, a címezési módokat és azokat a műveleteket, amelyeket a processzor végrehajthat. A vezérlőegység tervezése és működése szorosan összefügg az ISA-val, hiszen a CU feladata, hogy ezeket az utasításokat értelmezze és végrehajtsa.

Minden egyes utasítás az ISA-ban egyedi bináris kóddal rendelkezik (opcode), amelyet a vezérlőegységnek fel kell ismernie és dekódolnia kell. A dekódolási logika a CU-ban kifejezetten az adott ISA-hoz van tervezve. Ha az ISA megváltozik, a dekódolási logikát is módosítani kell. Ez a szoros kapcsolat mutatja, hogy az ISA nem csak a programozók számára fontos, hanem a hardvertervezők számára is alapvető referencia pontot jelent.

Két fő kategóriába sorolhatók az ISA-k, amelyek jelentősen befolyásolják a vezérlőegység tervezését:

- CISC (Complex Instruction Set Computer): A CISC architektúrák, mint például az Intel x86, gazdag és komplex utasításkészlettel rendelkeznek. Egyetlen CISC utasítás több alacsony szintű műveletet is végrehajthat, például memóriaolvasást, aritmetikai műveletet és eredményírását. Ez a komplexitás megkívánja a mikrokódos vezérlőegységeket. A CU-nak képesnek kell lennie arra, hogy egyetlen géputasítást több mikroutasítás sorozatává bontson, és ezeket szekvenciálisan végrehajtsa. A mikrokódos megvalósítás rugalmasságot biztosít, de lassabb lehet a mikrokód olvasása miatt.

- RISC (Reduced Instruction Set Computer): A RISC architektúrák, mint például az ARM vagy a MIPS, egyszerűbb, fix hosszúságú utasításkészlettel dolgoznak. Minden RISC utasítás általában egyetlen, atomi műveletet hajt végre (pl. csak összeadás, vagy csak memóriaolvasás). Ez az egyszerűség lehetővé teszi a hardveres huzalozású vezérlőegységek alkalmazását. A hardveres vezérlés gyorsabb, mivel nincs szükség mikrokód értelmezésére, de kevésbé rugalmas a változtatásokkal szemben.

A modern processzorokban gyakran találkozunk hibrid megoldásokkal. Például, az x86-os processzorok, bár alapvetően CISC ISA-t használnak, belsőleg gyakran mikro-operációkká (micro-ops) alakítják a komplex x86 utasításokat, és ezeket a mikro-operációkat egy RISC-szerű belső mag hajtja végre, gyakran hardveresen vezérelve. Ezt a folyamatot utasítás fordításnak (instruction translation) vagy mikroarchitektúrának nevezik, és a vezérlőegység egy speciális része (gyakran egy dedikált dekóder) felelős érte.

Az ISA és a CU közötti kapcsolat tehát alapvető. Az ISA határozza meg, mit kell tennie a vezérlőegységnek, a CU pedig a hardveres megvalósítás, amely ezt lehetővé teszi. A hatékony processzortervezéshez elengedhetetlen az ISA és a CU közötti szinergia, amely optimális teljesítményt és energiahatékonyságot biztosít.

Regiszterek szerepe a vezérlőegység működésében

A regiszterek kis méretű, rendkívül gyors tárolóegységek a processzoron belül, amelyek kulcsfontosságú szerepet játszanak a vezérlőegység működésében. Ezek a regiszterek ideiglenesen tárolják az adatokat, címeket és vezérlőinformációkat, amelyekre a vezérlőegységnek szüksége van az utasítások lehívásához, dekódolásához és végrehajtásához. Nélkülük a vezérlőegység nem lenne képes hatékonyan koordinálni a processzor tevékenységeit.

Néhány alapvető regiszter, amelyek szorosan kapcsolódnak a vezérlőegységhez:

- Programszámláló (Program Counter, PC): Ez a regiszter tárolja a következő végrehajtandó utasítás memóriacímét. A vezérlőegység a PC tartalmát használja az utasításlehívás fázisában, majd a lehívás után automatikusan növeli a PC értékét, hogy a következő utasításra mutasson. Elágazási vagy ugrási utasítások esetén a vezérlőegység írja felül a PC tartalmát a célcímre.

- Utasításregiszter (Instruction Register, IR): Az IR tárolja az éppen dekódolásra és végrehajtásra váró utasítást. Miután a vezérlőegység lehívta az utasítást a memóriából, az az IR-be kerül. A CU dekódolási logikája az IR tartalmát elemzi, hogy meghatározza a végrehajtandó műveletet és az operandusokat.

- Memóriacím-regiszter (Memory Address Register, MAR): A MAR tárolja annak a memóriacímnek az értékét, amelyre a processzor éppen írni vagy olvasni szeretne. A vezérlőegység tölti be a MAR-t a PC tartalmával utasításlehíváskor, vagy egy adatcím-regiszter tartalmával adatbetöltéskor/tároláskor. A MAR tartalma kerül a címbuszra.

- Memória adatregiszter (Memory Data Register, MDR): Az MDR ideiglenesen tárolja az adatot, amelyet a processzor a memóriából olvasott, vagy amelyet a memóriába írni szeretne. Amikor az utasítást lehívják, az MDR-be kerül, mielőtt az IR-be másolódna. Adatbetöltéskor az MDR-ből kerül az adat egy általános célú regiszterbe, íráskor pedig az MDR tartalma kerül a memóriába.

- Általános célú regiszterek (General-Purpose Registers, GPRs): Bár ezeket elsősorban az ALU használja az operandusok és eredmények tárolására, a vezérlőegység is felelős az adatok ezekbe a regiszterekbe történő beírásáért és kiolvasásáért az utasításoknak megfelelően. Az utasításdekódolás során a CU azonosítja, mely GPR-eket kell használni.

- Állapotregiszter (Status Register / Flags Register): Ez a regiszter különböző „flag”-eket (zászlók) tartalmaz, amelyek a legutóbbi aritmetikai vagy logikai művelet eredményének állapotát tükrözik (pl. nulla, negatív, túlcsordulás, előjel). A vezérlőegység használja ezeket a flag-eket elágazási utasítások (pl. „ugorj, ha nulla”) végrehajtásához, befolyásolva a programszámláló következő értékét.

A vezérlőegység a regiszterek tartalmának manipulálásával és a közöttük lévő adatmozgatás irányításával végzi el a fő feladatait. Például, az utasításlehíváskor a CU a PC tartalmát a MAR-be másolja, majd a memóriából kiolvasott adatot az MDR-be, végül az IR-be. Adatmozgatási utasításoknál a CU a megfelelő GPR-ek és a memória közötti adatátvitelt vezérli a MAR és MDR regisztereken keresztül. A regiszterek gyors hozzáférési ideje kritikus a processzor általános teljesítménye szempontjából, és a vezérlőegység hatékonysága nagyban függ attól, hogy mennyire optimálisan tudja kihasználni ezeket a belső tárolókat.

Az órajel és a vezérlőegység szinkronizációja

A processzorban minden művelet szigorúan időzített és szinkronizált, és ebben a folyamatban az órajel (Clock Signal) játssza a központi szerepet. Az órajel egy periodikus, négyszögjel alakú elektromos impulzus, amelyet egy órajelgenerátor állít elő. Ez a jel adja meg a processzor működési ritmusát, meghatározva, hogy mikor történhetnek meg a különböző műveletek. A vezérlőegység feladata, hogy az órajel ütemében koordinálja a processzor összes komponensét, biztosítva a hibátlan és szekvenciális működést.

Minden egyes órajelciklus (Clock Cycle) alatt a processzor egy meghatározott számú alacsony szintű műveletet hajthat végre. A vezérlőegység a dekódolt utasítás és az órajel alapján generálja a megfelelő vezérlőjeleket, amelyek aktiválják a processzor különböző funkcionális egységeit (pl. ALU, regiszterek, memória interfész). Például, egy utasításlehívás több órajelciklust is igénybe vehet: az első ciklusban a PC tartalma a MAR-ba kerül, a másodikban a memória címezése történik, a harmadikban az adat olvasása, stb. A vezérlőegység pontosan tudja, hogy melyik vezérlőjelet mikor kell aktiválnia az adott órajelciklusban.

A taktusfrekvencia (Clock Frequency), amelyet általában gigahertzben (GHz) mérnek, azt mutatja meg, hogy hány órajelciklust képes végrehajtani a processzor másodpercenként. Minél magasabb a taktuszfrekvencia, annál gyorsabban képes a processzor utasításokat végrehajtani, feltéve, hogy az utasításonkénti ciklusok száma (Cycles Per Instruction, CPI) nem nő aránytalanul. A vezérlőegység tervezésekor a mérnököknek optimalizálniuk kell a logikai áramköröket, hogy azok a lehető leggyorsabban reagáljanak az órajelre, minimalizálva a jelterjedési késéseket.

Az órajel a processzor szívverése, a vezérlőegység pedig a karmester, aki minden egyes lüktetésre pontosan összehangolja a komplex belső műveleteket.

A pipelining (futószalagos feldolgozás) technika tovább bonyolítja az órajel és a vezérlőegység kapcsolatát. A pipelining lehetővé teszi, hogy a processzor több utasítást dolgozzon fel egyidejűleg, különböző fázisokban. Míg az egyik utasítás a végrehajtási fázisban van, a következő már a dekódolási fázisban, a harmadik pedig a lehívási fázisban. A vezérlőegységnek ebben az esetben nem csak egyetlen utasítás ciklusát kell koordinálnia, hanem több párhuzamosan futó utasítás fázisait is, biztosítva, hogy ne legyenek adatfüggőségi vagy vezérlési függőségi problémák (hazards). Ehhez rendkívül kifinomult időzítési és szinkronizációs mechanizmusokra van szükség, amelyeket a vezérlőegység valósít meg.

A modern processzorokban az órajel-elosztó hálózatok (clock distribution networks) rendkívül komplexek, hogy biztosítsák az órajel pontos és szinkronizált eljutását a chip minden pontjára. A vezérlőegység szempontjából ez azt jelenti, hogy a vezérlőjelek generálása és eljuttatása a célkomponensekhez a lehető legpontosabban kell, hogy történjen, figyelembe véve az órajel terjedési késéseit. Az órajel és a vezérlőegység közötti szoros együttműködés a modern processzorok nagy teljesítményének alapja.

Pipelining és a vezérlőegység kihívásai

A pipelining, vagy futószalagos feldolgozás, egy kritikus teljesítménynövelő technika a modern processzorokban. Lényege, hogy az utasításciklust (Fetch, Decode, Execute, Write-Back) több, egymástól elkülönülő szakaszra bontja, és lehetővé teszi, hogy ezek a szakaszok párhuzamosan, különböző utasításokon dolgozzanak. Ez hasonló ahhoz, mint egy gyártósor, ahol egyszerre több termék készül, de mindegyik más-más fázisban van. Elméletileg a pipelining jelentősen növelheti az utasítások áteresztőképességét (Instructions Per Cycle, IPC).

Azonban a pipelining bevezetése komoly kihívásokat támaszt a vezérlőegység elé. A CU-nak nem csupán egyetlen utasítást kell irányítania, hanem több, különböző fázisban lévő utasítás párhuzamos végrehajtását kell koordinálnia. Ez a komplexitás számos problémát vet fel, amelyeket a vezérlőegységnek kezelnie kell:

1. Adatfüggőségek (Data Hazards)

Az adatfüggőség akkor lép fel, amikor egy utasításnak szüksége van egy korábbi, még nem teljesen végrehajtott utasítás eredményére. Például, ha az A utasítás összead egy számot, és az B utasítás ezt az eredményt használná fel, de az A utasítás még nem írta vissza az eredményt, akkor a B utasításnak várnia kell. A vezérlőegységnek fel kell ismernie ezeket a függőségeket, és be kell illesztenie buborékokat (stalls) a futószalagba, vagy operandus-előre továbbítás (forwarding/bypassing) technikával kell megoldania a problémát. Az előre továbbítás során az eredményt közvetlenül az ALU kimenetéről továbbítják a következő utasítás bemenetére, anélkül, hogy megvárnák a visszaírási fázist.

2. Vezérlési függőségek (Control Hazards / Branch Hazards)

A vezérlési függőség akkor merül fel, amikor egy elágazási utasítás (pl. IF-ELSE, FOR ciklus) megváltoztathatja a program végrehajtási sorrendjét. A vezérlőegység nem tudja előre, hogy az elágazás melyik ága fog végrehajtódni, amíg az elágazási utasítás el nem éri a végrehajtási fázist. Ha a CU rossz ágon folytatja a lehívást, akkor az előre lehívott és dekódolt utasításokat el kell dobni, ami jelentős teljesítményveszteséget okoz. Ennek kezelésére a vezérlőegység elágazás-előrejelzés (branch prediction) technikákat alkalmaz.

Az elágazás-előrejelző egység (Branch Predictor Unit), amely a CU része, megpróbálja előre jelezni, hogy az elágazás melyik úton fog tovább haladni. Ha az előrejelzés helyes, a futószalag megszakítás nélkül folytathatja a munkát. Ha téved, a vezérlőegységnek törölnie kell a rossz ágon lehívott utasításokat a futószalagból, és újra kell kezdenie a lehívást a helyes címről. Ez a „pipeline flush” jelentős büntetést (penalty) von maga után, mivel sok órajelciklus megy veszendőbe.

3. Strukturális függőségek (Structural Hazards)

Ezek akkor fordulnak elő, ha két vagy több utasítás ugyanazt a hardver erőforrást próbálja használni ugyanabban az órajelciklusban. Például, ha két utasítás egyszerre próbálna írni a memóriába, és csak egy memória port áll rendelkezésre. A vezérlőegységnek ebben az esetben is be kell iktatnia egy buborékot, vagy egy másik utasítást kell átütemeznie, hogy elkerülje az erőforrás-konfliktust.

A modern vezérlőegységek rendkívül kifinomult mechanizmusokkal rendelkeznek ezen kihívások kezelésére. Ide tartoznak az ütemezők (schedulers), a regiszter átnevezés (register renaming), az out-of-order execution (sorrenden kívüli végrehajtás) és a már említett elágazás-előrejelzés. Ezek a technikák lehetővé teszik, hogy a processzor a lehető legkevesebb leállással maximalizálja a futószalag kihasználtságát, és ezzel növelje a programok végrehajtási sebességét. A vezérlőegység tehát nem csupán irányít, hanem intelligensen optimalizálja is a végrehajtási folyamatot.

Cache memória és a vezérlőegység interakciója

A cache memória, vagy gyorsítótár, egy kis méretű, de rendkívül gyors memória, amely a processzor és a főmemória között helyezkedik el. Célja, hogy csökkentse a processzor és a lassabb főmemória közötti sebességkülönbséget, tárolva a gyakran használt adatokat és utasításokat a processzor közvetlen közelében. A vezérlőegység szorosan együttműködik a cache-el, felügyelve az adatfolyamot és biztosítva a gyorsítótár hatékony kihasználását.

Amikor a vezérlőegységnek egy utasítást vagy adatot kell lekérnie a memóriából (legyen szó akár utasításlehívásról, akár adatbetöltésről egy Load utasítás részeként), az első lépés mindig a cache memória ellenőrzése. Ezt a feladatot a memóriavezérlő egység (Memory Management Unit, MMU) egy része, a cache vezérlő (Cache Controller) végzi, amely szorosan integrálódik a vezérlőegységgel vagy annak utasításlehívási/adatbetöltési fázisát befolyásolja.

A cache működése és a vezérlőegység szerepe:

- Cache találat (Cache Hit): Ha a keresett adat vagy utasítás megtalálható a cache-ben, ez egy cache találat. Ebben az esetben a vezérlőegység rendkívül gyorsan hozzáférhet az adathoz a cache-ből, minimalizálva a késleltetést. A CU utasítja a cache vezérlőt, hogy adja át az adatot a megfelelő regiszternek (pl. IR az utasításoknál, GPR az adatoknál). Ez az ideális forgatókönyv, és a cache rendszer úgy van optimalizálva, hogy minél több találat legyen.

- Cache hiba (Cache Miss): Ha a keresett adat vagy utasítás nem található meg a cache-ben, ez egy cache hiba. Ebben az esetben a vezérlőegységnek le kell állítania a normál programfutást, és kezdeményeznie kell az adat betöltését a lassabb főmemóriából a cache-be. Ez magában foglalja a memória címzést, az adatblokk lekérdezését és annak a cache-be történő beírását. Ez a folyamat több órajelciklust is igénybe vehet, jelentős késleltetést okozva.

A vezérlőegységnek kezelnie kell a cache hibákat, ami gyakran magában foglalja a futószalag leállítását (stall) addig, amíg az adat be nem töltődik a cache-be a főmemóriából. Ezután az adatot a processzor azonnal felhasználhatja, és a futószalag folytathatja a munkát. A modern processzorok többszintű cache rendszereket használnak (L1, L2, L3 cache), és a vezérlőegységnek ezek közötti hierarchikus adatmozgást is koordinálnia kell.

A cache memória a processzor gyors memóriatára, ahol a vezérlőegység először keresi a szükséges utasításokat és adatokat, minimalizálva a lassabb főmemória elérésének idejét.

A cache koherencia fenntartása egy másik komplex feladat, különösen többmagos rendszerekben. Ha több mag rendelkezik ugyanazon adat másolatával a saját L1 cache-ében, és az egyik mag módosítja azt, a vezérlőegységeknek (vagy egy dedikált cache koherencia vezérlőnek) biztosítania kell, hogy a többi mag cache-ében lévő másolatok érvénytelenítve legyenek vagy frissüljenek. Ez megakadályozza, hogy a processzor inkonzisztens adatokkal dolgozzon. A vezérlőegység aktívan részt vesz a cache vezérlővel való kommunikációban, hogy ezeket a protokollokat betartassa.

A cache memória hatékony kezelése elengedhetetlen a modern processzorok teljesítményéhez. A vezérlőegység intelligenciája és a cache vezérlővel való szoros integrációja biztosítja, hogy a processzor a lehető leggyorsabban hozzáférjen a szükséges információkhoz, minimalizálva a memóriahozzáférési késéseket és maximalizálva az utasítások áteresztőképességét.

Interruptok és kivételek kezelése

A számítógép rendszerekben nem minden esemény történik a program által előre meghatározott, szekvenciális módon. Gyakran előfordulnak külső vagy belső események, amelyek azonnali figyelmet igényelnek, és megszakítják a processzor éppen futó programjának normális menetét. Ezeket az eseményeket megszakításoknak (interrupts) vagy kivételeknek (exceptions) nevezzük, és a vezérlőegység kulcsfontosságú szerepet játszik a kezelésükben.

Megszakítások (Interrupts)

A megszakítások általában külső események okozzák, amelyek a processzoron kívülről érkeznek, például egy I/O eszköz (billentyűzet, egér, merevlemez, hálózati kártya) jele, hogy egy művelet befejeződött, vagy adat áll rendelkezésre. A megszakítások lehetővé teszik, hogy a processzor ne kelljen folyamatosan ellenőriznie az I/O eszközöket (polling), hanem csak akkor reagáljon, amikor azok ténylegesen figyelmet igényelnek. Ez jelentősen növeli a rendszer hatékonyságát.

Amikor egy megszakítási jel érkezik a processzorra, a vezérlőegység feladata:

- Felismerés és nyugtázás: A CU érzékeli a megszakítási jelet, és nyugtázza azt az eszköz felé.

- Aktuális állapot mentése: Mielőtt bármilyen megszakítási rutint elindítana, a vezérlőegységnek el kell mentenie a processzor aktuális állapotát (pl. a programszámláló, regiszterek tartalmát) a verembe (stack), hogy a megszakítási rutin befejezése után a program ott folytathassa, ahol abbahagyta.

- Megszakítási vektor táblázat használata: A CU megkeresi a megszakítás típusához tartozó megszakítási vektor táblázatot (Interrupt Vector Table, IVT), amely tartalmazza a megfelelő megszakításkezelő rutin (Interrupt Service Routine, ISR) kezdeti címét.

- Ugrás az ISR-re: A vezérlőegység betölti az ISR címét a programszámlálóba, ezzel átadva a vezérlést a megszakításkezelő rutinnak.

- Visszatérés: Amikor az ISR befejeződik, a vezérlőegység visszaállítja a korábban elmentett processzor állapotot a veremből, és a program ott folytatja a futását, ahol a megszakítás előtt tartott.

Kivételek (Exceptions)

A kivételek belső események, amelyek a program végrehajtása során merülnek fel, és általában valamilyen hiba vagy rendellenes állapot jelzésére szolgálnak. Példák kivételekre:

- Osztás nullával: Az ALU egy osztás nullával műveletet próbál végrehajtani.

- Érvénytelen utasítás: A vezérlőegység egy olyan utasítást próbál dekódolni, amely nem szerepel az ISA-ban.

- Memóriahozzáférési hiba (Page Fault): A program olyan memóriaterülethez próbál hozzáférni, amelyhez nincs jogosultsága, vagy amely nincs fizikailag betöltve a memóriába.

- Túlcsordulás (Overflow): Egy aritmetikai művelet eredménye túl nagy ahhoz, hogy elférjen a regiszterben.

A kivételek kezelése hasonló a megszakításokhoz, azzal a különbséggel, hogy a kivételt okozó utasítás általában nem fejeződik be. A vezérlőegység azonosítja a kivétel típusát, menti az aktuális állapotot, és elugrik a megfelelő kivételkezelő rutinra. A kivételkezelő rutin megpróbálhatja kijavítani a hibát, vagy ha ez nem lehetséges, leállíthatja a programot és hibaüzenetet generálhat.

A vezérlőegység nem csupán a normális programfutást irányítja, hanem intelligensen reagál a váratlan eseményekre is, mint a megszakítások és kivételek, biztosítva a rendszer stabilitását és megbízhatóságát.

Mind a megszakítások, mind a kivételek kezelése kritikus a modern operációs rendszerek és alkalmazások számára. A vezérlőegység beépített logikája és hardveres támogatása elengedhetetlen ahhoz, hogy a processzor képes legyen hatékonyan és biztonságosan reagálni ezekre a váratlan eseményekre, fenntartva a rendszer integritását és a felhasználói élményt.

Multicore processzorok és a vezérlőegység

A modern processzorok túlnyomó többsége többmagos (multicore) architektúrájú, ami azt jelenti, hogy egyetlen fizikai chipen belül több független feldolgozóegység, azaz mag (core) található. Ez a megközelítés lehetővé teszi a párhuzamos feldolgozást, ahol több utasításfolyam (szál) futhat egyidejűleg, jelentősen növelve a teljesítményt. A többmagos rendszerekben a vezérlőegység szerepe még összetettebbé válik, mivel nem csupán egyetlen mag működését kell irányítania, hanem a magok közötti koordinációt és kommunikációt is kezelnie kell.

Minden egyes processzormag rendelkezik saját vezérlőegységgel. Ez azt jelenti, hogy egy kétmagos processzorban két független CU működik, egyenként felelős a saját magjának utasításlehívásáért, dekódolásáért és végrehajtásáért. Ennek ellenére a magoknak gyakran együtt kell működniük, és megosztott erőforrásokat (például L2/L3 cache, főmemória) kell elérniük. Itt lép be a képbe a rendszer szintű koordináció, amelyben a vezérlőegységeknek és a hozzájuk kapcsolódó architektúráknak központi szerepük van.

Kihívások a többmagos rendszerekben:

- Cache koherencia: Ahogy korábban említettük, a cache koherencia fenntartása kritikus. Ha több mag ugyanazon adat másolatával rendelkezik a saját cache-ében, és az egyik mag módosítja azt, a többi mag vezérlőegységének (vagy egy dedikált cache koherencia protokollnak) biztosítania kell, hogy az elavult másolatok érvénytelenítve legyenek. A vezérlőegységeknek képesnek kell lenniük erre a kommunikációra és szinkronizációra, gyakran snooping protokollok vagy címtáralapú protokollok segítségével.

- Memóriahozzáférés szinkronizáció: Amikor több mag próbálja elérni a főmemóriát, a vezérlőegységeknek koordinálniuk kell a hozzáférést, hogy elkerüljék a konfliktusokat és biztosítsák az adatok integritását. Ez magában foglalhatja a buszhozzáférés ütemezését és a memóriavezérlővel való kommunikációt.

- Megszakítások és kivételek kezelése: Egy többmagos rendszerben a megszakítások bármelyik magra érkezhetnek, vagy akár egy központi megszakításvezérlőn keresztül oszthatók el. A vezérlőegységeknek fel kell ismerniük, hogy melyik mag felelős az adott megszakítás kezeléséért, és hogyan kell átadni a vezérlést a megfelelő ISR-nek.

- Feladatok elosztása és ütemezés: Bár ez elsősorban az operációs rendszer feladata, a vezérlőegységeknek és a magoknak támogatniuk kell az OS-t a feladatok hatékony elosztásában és a szálak futtatásában. A vezérlőegységeknek képesnek kell lenniük a kontextusváltásra, azaz egy szál állapotának mentésére és egy másik szál állapotának betöltésére, amikor az OS átütemezi a feladatokat.

- Energiahatékonyság: A többmagos processzorok energiafelhasználásának optimalizálása szintén a vezérlőegységek feladata. Ez magában foglalhatja az egyes magok órajelének vagy feszültségének dinamikus szabályozását (dynamic voltage and frequency scaling, DVFS), vagy akár a nem használt magok kikapcsolását a teljesítményigénytől függően. A vezérlőegységeknek képesnek kell lenniük ezeknek a beállításoknak a monitorozására és adaptálására.

A többmagos processzorokban minden magnak megvan a saját vezérlőegysége, de a valódi kihívás a közös erőforrásokhoz való hozzáférés és a koherencia fenntartása, amit a vezérlőegységek közötti intelligens koordináció tesz lehetővé.

A modern többmagos processzorokban a vezérlőegységek közötti kommunikációt és koordinációt gyakran egy központi rendszervezérlő (System Agent vagy Uncore) egészíti ki, amely kezeli a memóriavezérlőt, a PCI Express interfészt és az L3 cache-t. Azonban még ebben az esetben is, az egyes magok vezérlőegységei felelősek a magon belüli finomhangolt vezérlésért és a külső vezérlővel való interakcióért. A többmagos architektúrák térnyerése rávilágít arra, hogy a vezérlőegység szerepe nem csupán az utasítások végrehajtására korlátozódik, hanem a teljes rendszer szintű hatékonyság és stabilitás biztosítására is kiterjed.

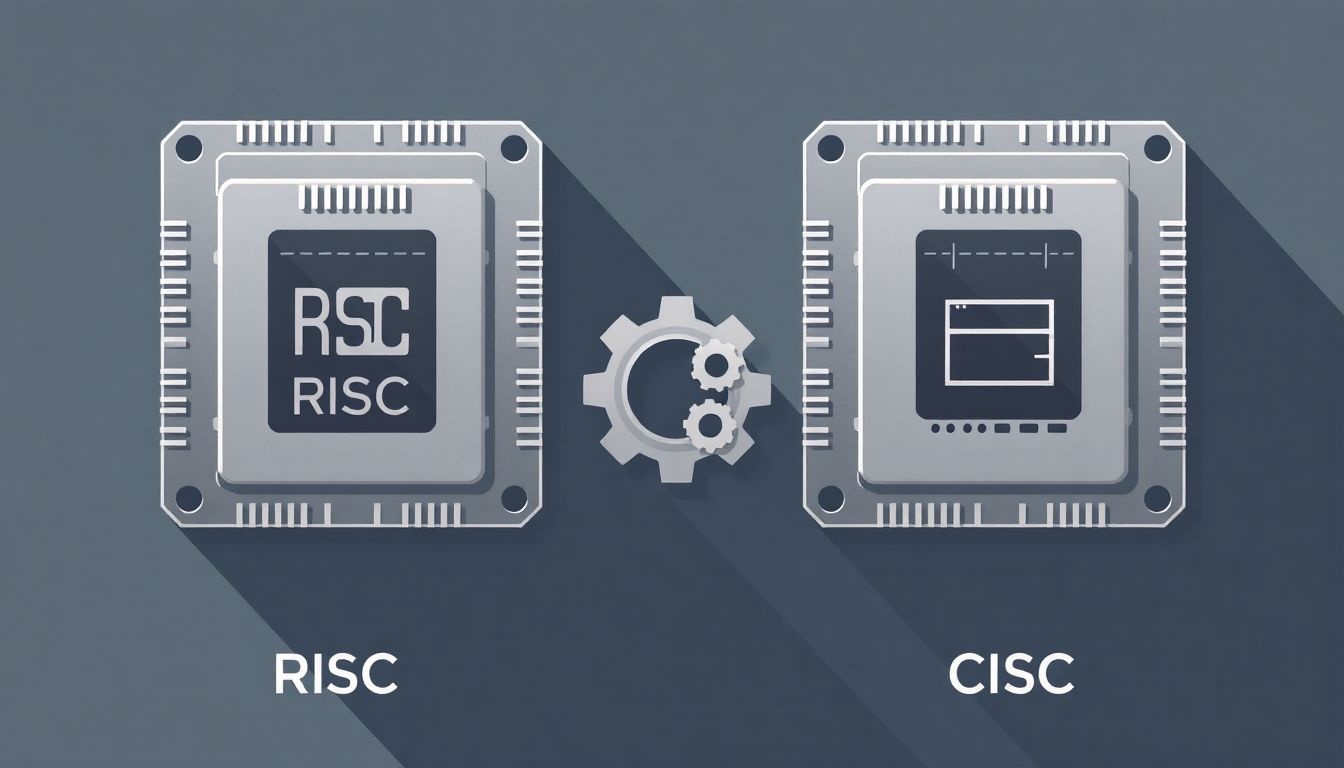

RISC vs. CISC architektúrák és a vezérlőegység

A processzorarchitektúrákat hagyományosan két fő kategóriába soroljuk: RISC (Reduced Instruction Set Computer) és CISC (Complex Instruction Set Computer). A vezérlőegység tervezése és komplexitása alapvetően különbözik ezen két megközelítés között, és ez jelentős hatással van a processzor teljesítményére, energiafogyasztására és rugalmasságára.

CISC (Complex Instruction Set Computer)

A CISC architektúrák, mint például az Intel x86 család, a komplex utasításkészletre fókuszálnak. Egyetlen CISC utasítás rendkívül sokrétű műveleteket hajthat végre, például memóriából adatot betölteni, aritmetikai műveletet végezni, majd az eredményt egy másik memóriacímre írni – mindezt egyetlen utasítás keretében. Ezen utasítások változó hosszúságúak lehetnek, és sokféle címezési módot támogatnak.

A CISC vezérlőegységek szinte kivétel nélkül mikrokódos megvalósítást használnak. Mivel egyetlen CISC utasítás több alacsony szintű műveletet foglal magában, a vezérlőegységnek le kell fordítania (dekódolnia) ezt az egy utasítást egy sorozatnyi egyszerűbb mikroutasításra. Ezek a mikroutasítások tárolódnak a vezérlő tárban (Control Store), és a CU egymás után hajtja végre őket. Ez a megközelítés:

- Rugalmas: Az utasításkészlet könnyen bővíthető vagy módosítható a mikrokód frissítésével.

- Könnyebb programozhatóság (gépi nyelven): Kevesebb utasítással végezhetők el komplex feladatok, ami egyszerűbbé teheti az assembly programozást.

- Komplexebb vezérlőegység: A mikrokódos vezérlés bevezet extra réteget (mikrokód lehívás, dekódolás), ami lassabb lehet, és a CU maga is nagyobb és komplexebb lehet a mikrokód tárolása és kezelése miatt.

RISC (Reduced Instruction Set Computer)

A RISC architektúrák, mint az ARM, MIPS vagy SPARC, az egyszerűsített utasításkészletre épülnek. A RISC utasítások jellemzően fix hosszúságúak, és minden utasítás egyetlen, atomi műveletet hajt végre (pl. csak betöltés, csak összeadás, csak tárolás). A komplexebb feladatokat több egyszerű RISC utasítás kombinációjával érik el.

A RISC vezérlőegységek gyakran hardveres huzalozásúak. Mivel az utasítások egyszerűek és fix hosszúságúak, a vezérlőjelek generálásához szükséges logikai áramkörök is egyszerűbbek és gyorsabbak lehetnek. Ez a megközelítés:

- Gyorsabb: Nincs szükség mikrokód olvasására és értelmezésére, a vezérlőjelek közvetlenül generálódnak.

- Egyszerűbb vezérlőegység: Kisebb, kevesebb tranzisztort igényel, ami alacsonyabb energiafogyasztást és gyártási költséget eredményezhet.

- Kevésbé rugalmas: Az utasításkészlet módosítása a hardver áttervezését igényli.

- Komplexebb fordítóprogramok: A fordítóprogramoknak kell optimalizálniuk a kódot, hogy a komplex feladatokat hatékonyan bontsák le az egyszerű RISC utasításokra.

| Jellemző | CISC (pl. x86) | RISC (pl. ARM) |

|---|---|---|

| Utasításkészlet | Komplex, sokrétű, változó hosszúságú utasítások | Egyszerű, atomi, fix hosszúságú utasítások |

| Vezérlőegység | Mikrokódos, komplex | Hardveresen huzalozott, egyszerűbb |

| Sebesség | Lassabb (mikrokód miatt) | Gyorsabb (direkt hardveres vezérlés) |

| Rugalmasság | Magas (mikrokód frissíthető) | Alacsony (hardveres módosítás szükséges) |

| Tranzisztorszám | Magasabb a CU-ban | Alacsonyabb a CU-ban |

| Energiafogyasztás | Magasabb | Alacsonyabb |

A modern processzorok gyakran hibrid megközelítést alkalmaznak. Például, az Intel x86 processzorok kívülről CISC ISA-nak tűnnek, de belsőleg egy komplex dekóder egység mikro-operációkká (micro-ops) fordítja a CISC utasításokat. Ezeket a mikro-operációkat aztán egy belső RISC-szerű mag hajtja végre, gyakran hardveresen vezérelve. Ez a technika lehetővé teszi a CISC ISA kompatibilitását a RISC-szerű magok sebességével és hatékonyságával. A vezérlőegység a dekóder és a végrehajtó egység közötti interfészt is kezeli, biztosítva a zökkenőmentes átalakítást és végrehajtást.

Modern vezérlőegységek fejlesztési trendjei

A vezérlőegységek (CU) a számítástechnika története során folyamatosan fejlődtek, és ez a trend a mai napig tart. A modern processzorok egyre komplexebbé válnak, és ezzel együtt a vezérlőegységekre is újabb és újabb kihívások hárulnak. A fejlesztési irányokat alapvetően a teljesítmény, az energiahatékonyság, a biztonság és a specializáció igénye határozza meg.

1. Energiahatékonyság

Az energiafogyasztás minimalizálása az egyik legfontosabb szempont a modern processzortervezésben, különösen a mobil eszközök és adatközpontok esetében. A vezérlőegységek kulcsszerepet játszanak ebben:

- Dinamikus feszültség- és frekvenciaszabályozás (DVFS): A vezérlőegységek monitorozzák a processzor terhelését, és ennek megfelelően dinamikusan állítják az órajelet és a tápfeszültséget. Alacsony terhelésnél csökkentik ezeket az értékeket, így energiát takarítanak meg.

- Részleges leállítás (power gating): A CU képes kikapcsolni a processzor nem használt részeit (pl. inaktív magok, ALU egységek) az energiafogyasztás további csökkentése érdekében.

- Hatékonyabb dekódolás és ütemezés: Az energiahatékonyabb algoritmusok a mikrokódos vezérlőegységekben és az ütemezőkben csökkentik a felesleges műveleteket és a tranzisztorok kapcsolgatását.

2. Biztonság

A biztonsági fenyegetések növekedésével a vezérlőegységeknek is szerepet kell játszaniuk a rendszer védelmében:

- Memóriavédelem: A CU kezeli a memóriahozzáférési jogosultságokat, biztosítva, hogy a programok csak a számukra kijelölt memóriaterületekhez férhessenek hozzá.

- Biztonságos végrehajtási környezetek (Secure Enclaves): Egyes processzorok dedikált biztonságos területeket (pl. Intel SGX) tartalmaznak, ahol a kód és az adatok elszigetelten futnak. A vezérlőegység felelős ezen környezetek felügyeletéért és a rajtuk kívüli hozzáférés megakadályozásáért.

- Spekulatív végrehajtás sebezhetőségeinek kezelése: A Spectre és Meltdown típusú támadások rávilágítottak a spekulatív végrehajtás biztonsági kockázataira. A modern vezérlőegységekbe olyan mikrokód frissítéseket és hardveres módosításokat építenek be, amelyek enyhítik ezeket a sebezhetőségeket, például a spekulatívan végrehajtott adatok szivárgásának megakadályozásával.

3. Mesterséges intelligencia (AI) és gépi tanulás (ML) integrációja

Az AI és ML feladatok robbanásszerű növekedése új kihívásokat és lehetőségeket teremt a vezérlőegységek számára:

- Speciális utasításkészletek: A modern vezérlőegységeknek támogatniuk kell az AI/ML feladatokhoz optimalizált speciális utasításokat (pl. vektorizált műveletek, mátrixszorzás), amelyek gyorsítják a neuronhálózatok futtatását.

- Dedikált gyorsítók vezérlése: Sok processzor tartalmaz dedikált AI gyorsítókat (pl. NPU-k, GPU-k). A fő processzor vezérlőegységének képesnek kell lennie ezeknek a gyorsítóknak az inicializálására, az adatok átadására és a végrehajtásuk koordinálására.

- Öntanuló CU-k: Kutatások folynak olyan vezérlőegységek kifejlesztésére, amelyek gépi tanulási algoritmusokat használnak az elágazás-előrejelzés, az utasításütemezés és az erőforrás-elosztás optimalizálására, dinamikusan alkalmazkodva a futó programok viselkedéséhez.

4. Moduláris és elosztott vezérlés

A „chiplet” alapú architektúrák térnyerésével (ahol a processzor több kisebb, dedikált chipletből épül fel) a vezérlőegységek is egyre inkább modulárissá és elosztottá válnak. Ez lehetővé teszi a specializált vezérlők integrálását az egyes chipletekbe, és egy magasabb szintű vezérlőréteg koordinálja a különböző modulok működését.

A vezérlőegység tehát nem egy statikus komponens, hanem egy dinamikusan fejlődő entitás, amely folyamatosan alkalmazkodik a számítástechnika új kihívásaihoz és igényeihez. A jövőben még intelligensebb, energiahatékonyabb és biztonságosabb vezérlőegységekre számíthatunk, amelyek alapvetően formálják a következő generációs processzorok képességeit.

A vezérlőegység hibái és azok hatásai

A vezérlőegység (CU) a processzor legkritikusabb komponensei közé tartozik. Mint minden komplex elektronikai áramkör, ez is hajlamos a hibákra, amelyek súlyos következményekkel járhatnak a rendszer működésére nézve. A CU hibái a szoftveres hibáktól eltérően gyakran nehezen diagnosztizálhatók, mivel a processzor alapvető működését érintik. A hibák eredhetnek gyártási anomáliákból, öregedésből, sugárzásból vagy akár szoftveres mikrokódhibákból.

A vezérlőegység hibáinak típusai és következményei:

-

Utasításdekódolási hibák:

- Tünetek: A processzor érvénytelen utasításokat próbál végrehajtani, vagy helytelenül értelmez egy érvényes utasítást. Ez gyakran érvénytelen opkód kivételhez (invalid opcode exception) vagy véletlenszerű összeomlásokhoz (random crashes) vezet.

- Hatás: A programok hibásan futnak, vagy azonnal összeomlanak. A rendszer instabillá válik, és gyakori kékhalál (BSOD) vagy kernel pánik (kernel panic) jelenségek léphetnek fel. A felhasználó számára ez egy teljesen kiszámíthatatlan viselkedést jelent.

-

Vezérlőjel-generálási hibák:

- Tünetek: A vezérlőegység rossz időben, rossz sorrendben, vagy helytelen logikai értékkel generál vezérlőjeleket. Például, az ALU-nak küldött jel nem az összeadást, hanem a kivonást aktiválja.

- Hatás: Az adatok sérülnek, a számítások eredményei hibásak lesznek. Ez súlyos adatvesztést vagy rendszerszintű inkonzisztenciát okozhat, ami nehezen felderíthető hibákhoz vezethet az alkalmazásokban vagy az operációs rendszerben.

-

Időzítési hibák:

- Tünetek: A vezérlőegység nem képes szinkronban tartani a processzor különböző részeit az órajellel. Például, egy regiszterbe írás túl későn történik meg, és a következő órajelciklus már a régi értéket olvassa ki.

- Hatás: Hasonlóan a vezérlőjel-generálási hibákhoz, ez is adatkorrupcióhoz és kiszámíthatatlan viselkedéshez vezet. A rendszer instabilitása és alkalmankénti lefagyások is gyakoriak.

-

Programszámláló (PC) kezelési hibák:

- Tünetek: A CU hibásan növeli a PC értékét, vagy rossz címet tölt be elágazási utasításoknál.

- Hatás: A program „elugrik” egy nem létező vagy rossz memóriacímre, ami azonnali programösszeomlást vagy rendszerösszeomlást okoz. Ez a szegmentálási hiba (segmentation fault) vagy védelmi hiba (general protection fault) egyik fő oka lehet.

-

Mikrokódhibák (mikrokódos CU esetén):

- Tünetek: A mikrokód hibásan van megírva vagy sérült, ami helytelen mikroutasítás-sorozatokat eredményez.

- Hatás: Ez rendkívül széles spektrumú hibákat okozhat, az enyhe teljesítménycsökkenéstől a súlyos adatkorrupcióig és rendszerösszeomlásokig. A mikrokódfrissítések néha javítják, néha pedig bevezetik ezeket a hibákat.

A vezérlőegység hibái a processzor működésének alapjait rázzák meg, a legapróbb anomália is katasztrofális adatsérülést vagy rendszerszintű összeomlást okozhat.

Diagnosztika és megelőzés:

A CU hibáit nehéz diagnosztizálni, mivel a hiba forrása mélyen a hardverben van. Általában speciális diagnosztikai eszközökkel, mint például a memtest (bár ez elsősorban RAM-ot tesztel, a CPU hibái is megmutatkozhatnak rajta keresztül), vagy a gyártók által biztosított CPU diagnosztikai szoftverekkel lehet feltárni. A megelőzés szempontjából a gyártási folyamat minőségellenőrzése, a stressztesztelés, és a mikrokód frissítések (amelyek gyakran hibajavításokat is tartalmaznak) kulcsfontosságúak. Az ECC (Error-Correcting Code) memória használata segíthet a memória hibáinak korrigálásában, de a CU belső hibáit nem tudja kezelni.

Összességében a vezérlőegység hibái az egyik legkomolyabb problémát jelentik egy számítógépes rendszerben, mivel a processzor alapvető működését érintik, és a rendszer instabilitásához, adatvesztéshez vagy teljes működésképtelenséghez vezethetnek.

Jövőbeli kihívások és innovációk a vezérlőegységek tervezésében

A számítástechnika folyamatosan fejlődik, és ezzel együtt a vezérlőegységek (CU) tervezői is újabb és újabb kihívásokkal néznek szembe. Ahogy a Moore-törvény lassul, és a hagyományos teljesítménynövelési módszerek korlátaikhoz érnek, az innovációra egyre nagyobb hangsúly kerül, különösen a vezérlési logika terén. A jövőbeli trendek és kihívások a következők:

1. Heterogén architektúrák és specializált gyorsítók vezérlése

A modern rendszerek egyre inkább heterogén architektúrákra épülnek, ahol a CPU mellett dedikált gyorsítók (GPU-k, NPU-k, FPGA-k, DSP-k) végzik a speciális feladatokat. A vezérlőegységnek képesnek kell lennie ezeknek a különböző típusú feldolgozóegységeknek a hatékony koordinálására. Ez magában foglalja az adatok átadását a CPU és a gyorsítók között, a feladatok ütemezését a megfelelő egységre, és a végrehajtás szinkronizálását. Ez egy sokkal összetettebb vezérlési problémát jelent, mint egy homogén CPU mag vezérlése.

2. In-memory computing és a vezérlés decentralizálása

Az in-memory computing (memórián belüli számítás) paradigmája, ahol a számítási feladatokat a memóriaegységek közelében vagy akár magában a memóriában végzik, újradefiniálhatja a vezérlőegység szerepét. Ebben az esetben a központi CU helyett decentralizált, kisebb vezérlőegységekre lehet szükség a memória modulokon belül, amelyek a helyi számításokat irányítják. Ez alapvetően változtatja meg a hagyományos Neumann-architektúrát, és új vezérlési protokollokat igényel.

3. Kvantumszámítástechnika

Bár a kvantumszámítógépek működési elve gyökeresen eltér a klasszikus számítógépekétől, a kvantumprocesszoroknak is szükségük van valamilyen vezérlőmechanizmusra. A kvantum vezérlőegységek feladata a qubit-ek állapotának manipulálása, a kvantumkapuk alkalmazása és a kvantumalgoritmusok végrehajtásának koordinálása lesz. Ez egy teljesen új terület, ahol a „vezérlőegység” fogalma is új értelmet nyerhet, figyelembe véve a kvantummechanika elveit.

4. Energiahatékonyság határainak feszegetése

Ahogy a tranzisztorméret zsugorodik, az energiafogyasztás és a hőtermelés kritikus tényezővé válik. A vezérlőegységeknek még intelligensebb módon kell kezelniük az energiaellátást, például sub-threshold computing (küszöbfeszültség alatti számítás) vagy near-threshold computing (küszöbfeszültség közeli számítás) technikákkal, amelyek rendkívül alacsony feszültségen működnek, de növelik a zajérzékenységet. A CU-nak képesnek kell lennie a hibák és a zaj kezelésére is ezekben az extrém energiahatékony üzemmódokban.

5. Mesterséges intelligencia a vezérlésben

Ahogy korábban említettük, a gépi tanulás alkalmazása a vezérlőegység belső működésének optimalizálására egyre inkább teret nyer. Az öntanuló vezérlőegységek képesek lehetnek adaptálni az elágazás-előrejelzési stratégiáikat, dinamikusan optimalizálni a futószalagot, vagy akár előre jelezni a memóriaigényeket, a futó programok viselkedése alapján. Ez egy olyan „intelligens” vezérlést tesz lehetővé, amely túlszárnyalja a statikus, előre programozott logikát.

A jövő vezérlőegységei túllépnek a merev logikán; adaptív, öntanuló rendszerekké válnak, amelyek képesek lesznek koordinálni a heterogén számítási környezeteket, a kvantumprocesszorokat és a memórián belüli feldolgozást.

6. Robusztusság és hibatűrés

A modern processzorok egyre nagyobb tranzisztorszámával és a kisebb gyártástechnológiákkal nő a hibák valószínűsége. A vezérlőegységeknek beépített hibatűrő mechanizmusokkal kell rendelkezniük, amelyek képesek észlelni és korrigálni a belső hibákat, mielőtt azok a rendszer instabilitásához vezetnének. Ez magában foglalhatja a redundáns logikát, a hibajavító kódokat és a dinamikus konfigurálhatóságot.

A vezérlőegység jövője izgalmas és kihívásokkal teli. Ahogy a számítógépek paradigmái változnak – a hagyományos CPU-któl a specializált gyorsítókig, a kvantumprocesszorokig és az in-memory computingig –, úgy kell a vezérlési logikának is alkalmazkodnia és megújulnia. Az innovációk ezen a területen alapvetően formálják majd a következő generációs számítástechnikai rendszerek képességeit és hatékonyságát.